### **Ultimo Series of Hardware Design Manuals**

The Ultimo series card is a network interface card. Its main interface functions include one 100-megabit network interface, a reserved I2S/TDM audio interface for control and monitoring or for transparent transmission of custom data packets, and a UART interface for controlling and monitoring or for transmitting custom data packets. It is mainly applied in dual-channel or quad-channel audio transceivers.

Main features of the module: Utilizing the most advanced module technology, it offers you a network audio transmission solution in a faster and more cost-effective manner. With the features of automatic device discovery, label-based signal wiring, and plug-and-play operation, it provides excellent audio performance through a freely shared standard network.

#### Audio function

Sampling rate 44.1/48/88.2kHz

Audio channel input/output 2x2 Channels, 4x4 Channels

Digital audio format TDM 12S

Audio transmission format Transmitting audio via IP and AES67

Sampling bit depth 16/24/32 Bit

Clock Built-in word clock or external word clock

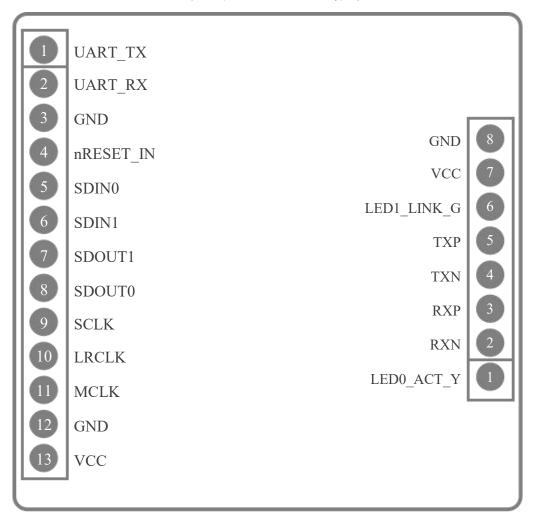

Figure 1 (Top View)

## 1. Pin description

| Туре | Description    |

|------|----------------|

| IO   | Input/Output   |

| DI   | Digital input  |

| DO   | Digital output |

| PI   | Power input    |

| PO   | Power output   |

| AI   | Analog input   |

| AO   | Analog output  |

| OD   | Open Drain     |

Table 1 (Description of IO Parameter Types)

Figure 2 Pin Definitions

The following table lists the specific types and definitions of the pins. The number of pins for terminal J8 is 13, and for J10 it is 8. For detailed information, please refer to the pin description in Figure 1.

| J8 No. (13P) | Pin type | Name             | I/0 | Description         | DC<br>Characteristics | Note |

|--------------|----------|------------------|-----|---------------------|-----------------------|------|

| 13           | POWER    | VCC              | ΡI  | Power module        | Vnorm=3.3V            |      |

| 3, 12        |          | GND              | PΙ  | GND                 | Vnorm=0V              |      |

| 4            | RST      | nRESET_IN        | DI  | Force Card Reset    |                       |      |

| 1            | UART     | CMOS_RS_232_TX_A | DO  | UART A              |                       |      |

| 2            |          | CMOS_RS_232_RX_A | DI  |                     |                       |      |

| 9            |          | SCLK             | DO  | Audio I2S/TDM Clock | 3.3V Level            |      |

| 10           | I2S/TDM  | LRCLK            | DO  | Left Right Clock    | 3.3V Level            |      |

| 11           |          | MCLK             | DO  | Master Clock Output |                       |      |

| 8            |          | SDOUT0           | DO  | Audio I2S/TDM Out   |                       |      |

| 7            |          | SDOUT1           | DO  |                     |                       |      |

| 5            |          | SDIN0            | DI  | Audio I2S/TDM In    |                       |      |

| 6            |          | SDIN1            | DI  | Audio 125/IDM III   |                       |      |

| J10 No. (8P) | Pin type | Name        | I/0 | Description       | DC<br>Characteristics | Note |

|--------------|----------|-------------|-----|-------------------|-----------------------|------|

| 7            | POWER    | VCC         | PI  | Power module      | Vnorm=3.3V            |      |

| 8            |          | GND         | PΙ  | GND               | Vnorm=0V              |      |

| 1            | LI/O     | LEDO_ACT_Y  | DI  | LED Indication    |                       | PU   |

| 6            |          | LED1_LINK_G | DI  | LED INGICATION    |                       | PD   |

| 5, 4         | MDI      | TXP、TXN     | 10  | Differential pair |                       |      |

| 3, 2         |          | RXP、RXN     | IO  | Differential pair |                       |      |

Table 2 Pin Description

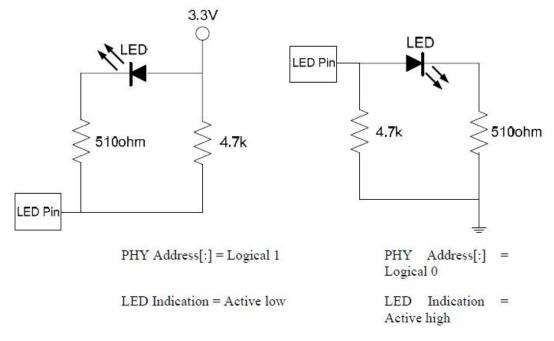

Figure 3 LED and PHY Address Configuration

Note: 1. LED0 Default PU,LED1 Default PD;

2. PHY Address is 0x01.

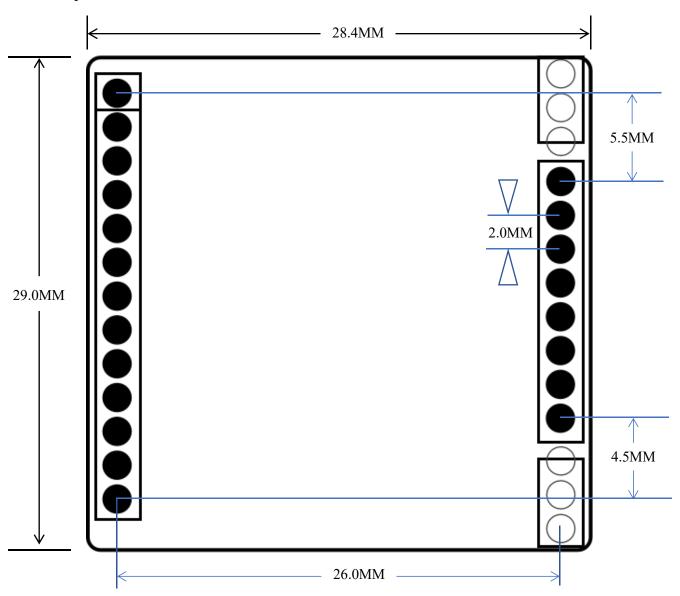

# 1. Physical scale

Figure 4 Physical dimensions of the module

# 3. History version record

| Version | Revise content                                  | Release time       |

|---------|-------------------------------------------------|--------------------|

| A0      | First draft released                            | December 1st, 2019 |

| A1      | Update the product the pin definition diagrams. | May 31st, 2023     |

Table 3 (Historical Version Record Table)